摘要:本文分析讨论了高速PCB板上由于高频信号的干扰和走线宽度的减小而产生的电源噪声和 压降,并提出了高速PCB的电源模型,采用电源总线网络布线,选取合适的滤波电容,模拟数字地 分开等几个简单有效的方法来解决高速PCB板的噪声和压降问题。

0 引言

随着集成电路工艺和集成度的不断提高,集成电路的工作电压越来越低,速度越来越快。进入新世纪后,CPU和网络都迈入了GHZ的时代,这对于PCB板的设计提出了更高的要求。本文正是基于这种背景下,对高速PCB设计中最重要的环节之一——电源的合理布局布线进行分析和探讨。

1 电源模型分析

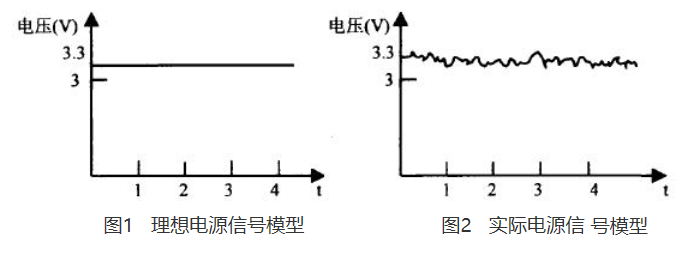

通常,在进行理论上的分析和计算时,都是把电源进行理想化,即电源无内阻,也无寄生阻抗。如果用一个3.3V的电压源对PCB上的元件供电,那么无论距离电源的远近,各个元件都应工作在3.3V,且没有噪声。然而在实际的设计工作中,由于PCB上的Ic和输入输出的信号都工作在高频下,电场和磁场的相互转化,必不可免的给电源引入了噪声,如图1、图2所示。同时由于PCB板上的走线非常的细,又产生了由于线路阻抗引起的压降,使远离电压源的器件工作电压小于电源电压。因而高速PCB的电源布线存在两个关键的问题:电源噪声和压降。

2 电源线的合理布局

设计高速PCB板的关键之一就是要尽可能的减小由于线路阻抗引起的压降和高频电磁场转换而引入的各种噪声。通常用两种方法来解决上述问题。一是电源总线技术(POWER BUS),另一种方法就是采用一个单独的电源层进行供电。后者在很大程度上缓解了压降和噪声的问题,但考虑到多层PCB的工艺复杂,昂贵的费用和较长的制作周期,一般设计者们更喜欢采用前者,因而有必要对电源总线的合理布线进行分析讨论。

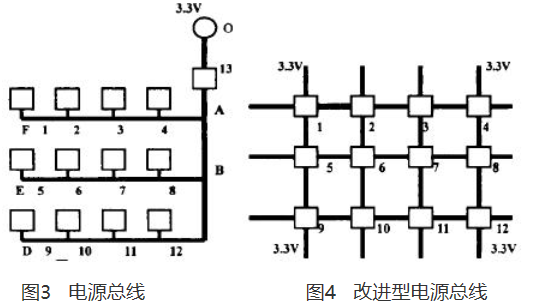

如图3所示,采用了电源总线技术,各个元器件悬挂在电源总线上,所以又称之为悬挂式总线,电源总线的宽度通常比普通的信号线要宽,采用总线技术后,虽然可以减小压降和和噪声的问题,但它们仍然存在的。

首先来看压降问题,假设电源电压为3.3V,0A,AB,BC,CD,BE,AF各段导线的电阻为0.05Ω,PCB板上的每个元器件的扇出或吸入电流为200ma,并作两个理想假定:

1.不考虑由于A,B,C处电源线地突然拐角而产生的电压电流突变;

2.不考虑边界元件(1,4,9,12)由于电磁场地相互转换而引起的边界效应。

则导线OA中的电流为2.6A,导线.AB中的电流为1.6A,导线BC和CD中的电流为0.8A,最后元件9上的电压为:

3.3-2.6×0.05-1.6×0.05-0.8×0.05=3.01V

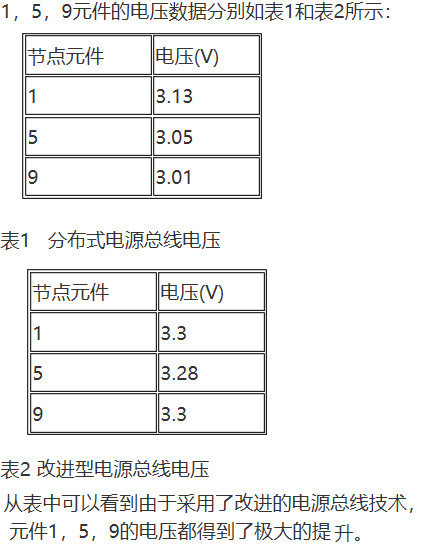

由于线路的阻抗产生了0.29V的压降,偏差几乎达到10%,这对于一个3.3V的电压来说已经是相当大了,而且随着IC朝低电压方向的发展,已经有很多工作在2.5V乃至更低的Ic,因此这样大的压降将是非常致命的。同时,在这种电源总线下,噪声也是一个很大的问题,如图3,每个器件产生的噪声都将通过电源耦合到元件13中,这也就是说器件13叠加了13个元件的噪声,这将很容易引起器件13不能正常工作。由于这两个问题依然存在,因此对电源总线技术进行了改进,如图4所示,它被称为电源总线网络法,即让电源总线相互交叉,而把对噪声和压降敏感的元件放在电源线网络的交叉点上,使得每一个元件同时属于几个不同的回路,如图4中的元件6,7就分别属于四个不同的小回路。由于电流可以从网络中的任何一条总线上进来或出去,而且每一个网孔构成了一个回路,这就不仅可以使网络中每条总线上的电流趋于均衡,不会出现悬挂式总线上的各段总线电流大小不一致的问题,因此就可以减小由于线路阻抗引起的压降问题。元件的电流由各网孔417/分担,每个网孔的电流为400mA。对于元件5,元件9和元件1的电压都比它高,因而电流从元件1和9流向5,从5流出到6。在最坏情况下即元件9和1的电流全部从一端流出进入元件5,则元件5上的电压为3.3-0.4×0.05=3.28V(仍假定各段导线电阻为0.05Ω),要比悬挂式总线高了许多。悬挂式电源总线和改进型电源总线中元件1,5,9元件的电压数据分别如表1和表2所示:

同时对于各个元件产生的噪声来说:由于干扰是高频信号,因而每个回路可以看成一个单匝线圈。根据法拉第电磁感应定律ξ=dφ/dt,由于每个回路中的电流方向不一样,因而产生的变化磁场(大小为穿过每个网孔的磁通φ)的方向也就不一致,因而感应的电动势的方向也就不一致,这样就可以起到相互抵消的作用,减小了由于噪声干扰产生的尖锋电压或电流,保护了元件的正常工作。同时由于电源总线网络是杂乱无章的,因而每个元器件产生的噪声通过电压平均的耦合到其它各个元器件上去,最终减小了远端器件的压降和近端器件的噪声问题(相对电源而言)。改进的电源网络总线技术不仅对宏观的PCB十分有效,对微观的大规模集成电路中的电源的布线也具有一定的参考价值。

3 滤波电容的选取与放置

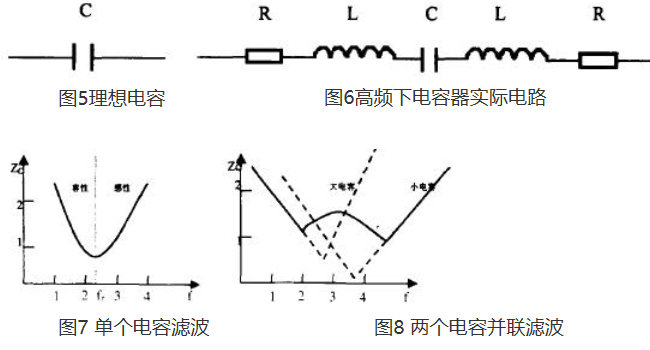

虽然采用了改进的电源总线技术后可以在很大程度上减小噪声的问题,但它总是存在的,这就必然要求引入电容器进行滤波。电容器的种类有很多,由于制造的材料和工艺的不同,各种电容器的滤波性能不尽相同。同时在高频下,电容本身也会产生寄生的阻抗。如图5,图6所示。因而在高频下,电容本身成了一个谐振电路,谐振频率:fr=1/(2π√LC)。由于寄生阻抗的存在,当电容器的工作频率f>fr时电容呈现感性,f<fr时,电容呈现容性,如图7所示。因而在选择滤波电容是要特别小心,要尽量使电容工作在容性状态,如果电容选取不当,使电容工作在感性状态,那么也就失去了滤波的作用。因此一定要选取电容值(C)大,串联电阻(R)和串联电感(L)小的电容器。由于制造材料的不同,各种电容的参数也不同,一般来说,电解电容和胆电容对低频噪声的滤波效果比较好,瓷片电容,独石电容等对高频噪声的滤波效果比较好。在实际的PCB板的设计中,滤波常分为两个部分,电源滤波和器件的滤波。对于电源,由于整个PCB板上的噪声都加到了它的上面,其中不仅包含了低频噪声,也包含了大量的高频噪声。为了有效的滤除这些噪声,通常是采用一个大电容(典型为>uF的电解电容或胆电容)和一个小电容(典型为uF)并联来进行滤波,这样可以极大的提高滤除的噪声范围,如图8所示。对于器件滤波,随着集成电路工艺的进步,IC自己本身能较好的抑制低频噪声,而对高频噪声比较敏感,所以一般采用小电容(典型为pF)来进行电源滤波。

4 数字地和模拟地

随着Ic集成度的提高,现在的IC一般都有好几对电源和地,其中就有模拟地和电源地。地线实际上也是一条信号线,但它的特殊性在于它是电路的公共端,通常是指零电位点。但由于使用的导线和敷铜连线在高频下都有寄生的电感,电容的存在,将当其用作地线时,导线本身的阻抗也会是电容产生公共耦合,从而使模拟地和数字地相互干扰。由于数字信号的0,1有一定的容差范围,如0.7v以下为0,2.4V以上为1,所以数字信号上有几百毫伏的噪声一般是不会影响信号的正常判断的。而模拟信号对噪声十分敏感,如果一个幅度为2V的正弦信号上叠加了一个几百毫伏的噪声,再经过多级放大器放大后,那么很有可能引起信号门限电平的误判而使这个电路工作在错误的状态之下。所以从理论上来说要将数字地和模拟地分开,以降低电源对噪声的耦合作用。在实际的设计中,通常把电源通过两个uH的电感引出分别作为模拟电压和数字电压,同时在电源的地端用一个零欧姆的电阻分别引出作为模拟地和数字地。

5结束语

在对高速PCB上的电源存在的两个问题——压降和噪声的产生原因进行了分析,并就如何在高速PCB的实际设计中有效地解决这两个问题提出了一些方法,在实际的设计工作中当然还有其它的解决方法,不一一例举。总之,在设计高速PCB板时,对电源布局布线的处理应尽量遵循下面一些规则:

1.有条件的情况下,尽量采用单独的电源层和地层进行供电。采用电源网络总线时,网孔越多越好,形成许多嵌套的网孔,同时总线要尽量的宽,以达到均衡电流,降低噪声的目的;

2.电源的走线不能中间细两头粗,以免在上面产生过大的压降。走线不能突然拐弯,拐弯要采用大于90°的钝角,最好采用圆弧形走线,电源的过孔要比普通的人一些。有条件的话,在过孔处加滤波电容;

3.对于那些特别容易产生噪声的部分用地线包围起来,以免产生的噪声耦合入电压。