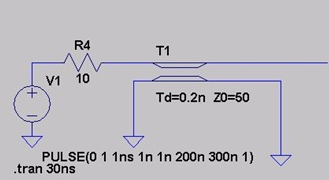

一般来说,当传输线很短时,传输延时在一定的范围内,此时虽然仍然存在反射,但反射的波形在信号的上升沿之内,则从波形看,没有大的影响,但究竟传输延时短到什么程度才算短呢?我们做一个实验,还是通过spice仿真得到结果。图1为仿真电路图,该信号源端上升时间为1ns,幅度为1V,阻抗为10欧姆。

图1 仿真电路图

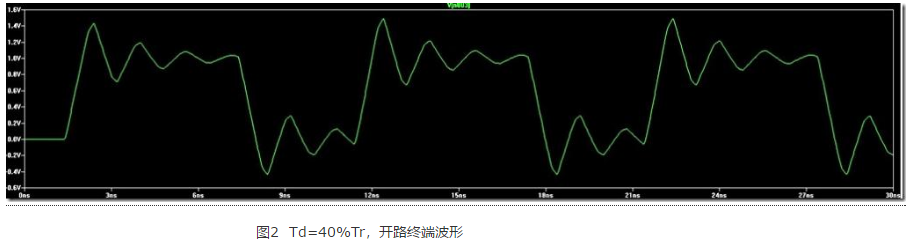

1、Td=40%Tr(Tr为上升时间,Td为传输延时),开路终端波形。

图2 Td=40%Tr,开路终端波形

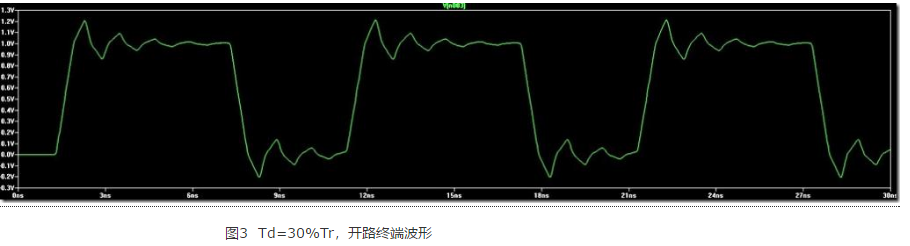

2、Td=30%Tr(Tr为上升时间,Td为传输延时),开路终端波形。

图3 Td=30%Tr,开路终端波形

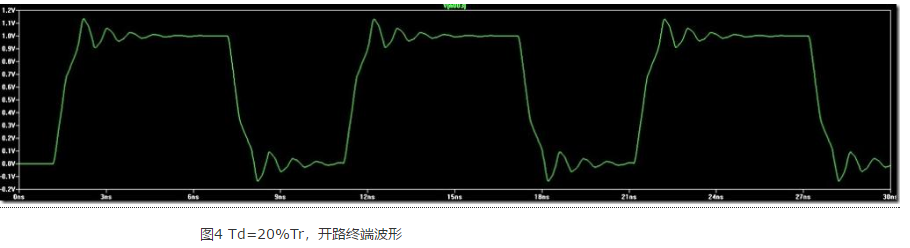

3、Td=20%Tr(Tr为上升时间,Td为传输延时),开路终端波形。此时的过冲约为0.11V,为信号幅度的11%。

图4 Td=20%Tr,开路终端波形

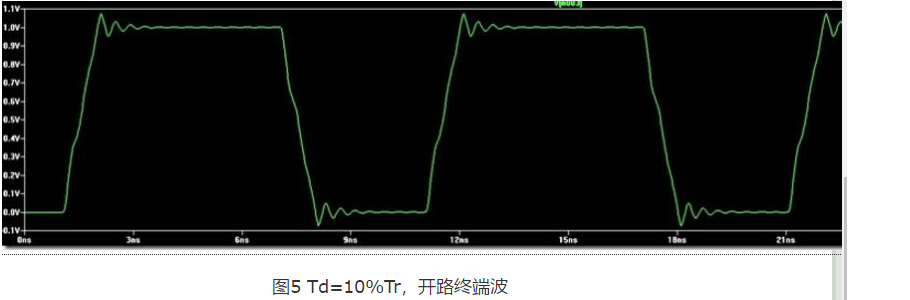

4、Td=10%Tr(Tr为上升时间,Td为传输延时),开路终端波形。

图5 Td=10%Tr,开路终端波

由仿真可知,信号的过冲和传输线的时延有关,《信号完整性分析》中描述说,“当传输线延时Td>信号上升时间的20%时,就要开始考虑由于导线没有终端端接而产生的振铃噪声。当时延大于上升时间的20%时,振铃会影响电路功能,,必须加以控制,否则这是造成信号完整性问题的隐患。吐过Td<20%信号的上升时间,振铃噪声可以忽略,传输线不需要终端匹配。”

所以,又出现了无敌的经验法则:为了避免信号完整性问题,没有端接的传输线的最大长度为,Len < Tr(Tr表示信号上升时间,Len的单位为in)。换算成mil就是乘个1000——是否进行阻抗匹配端接阻容依据。

很悲剧的是,在目前的高速电路中,信号的上升时间已经小于0.25ns,所以Len为0.25in(=6.35cm),一般来说,PCB上走线的距离很容易大于这个值,所以,必须对电路进行端接设计,同理1ns的上升时间,当线长超过1in=25.4cm时就需要加串联电阻进行阻抗匹配。

版权*转载申明:

本站内容为本站编辑或整理,所以转载务必通知本站并以超链接形式注明内容来自本站,以免带来不必要麻烦。引文出处:https://www.cnblogs.com/chenman/p/3643698.html