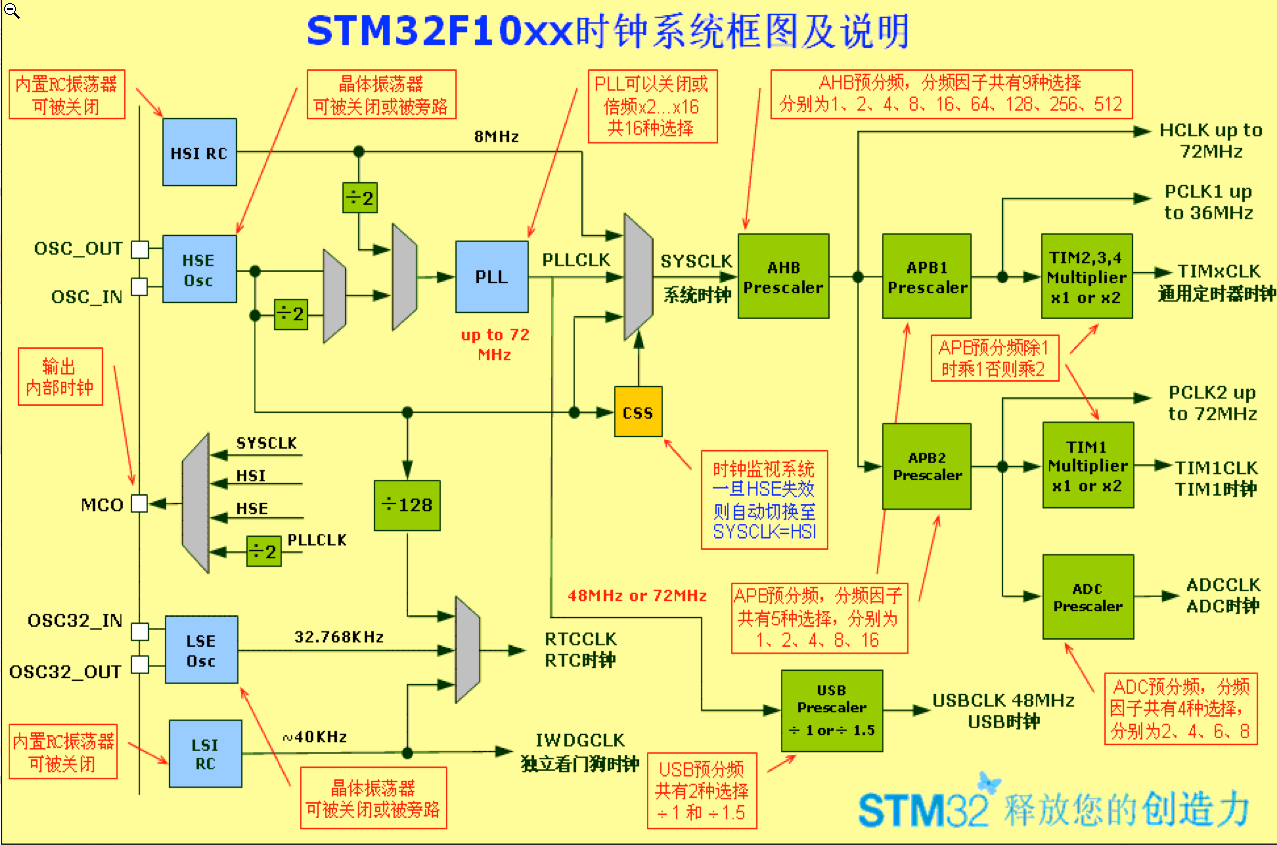

一,时钟系统框图

下面我们根据这张图说说有关STM32时钟系统的那些事

二,STM32的5个时钟源:HSI HSE LSI LSE PLL

1. HSI:高速内部时钟

由内部RC振荡器产生,频率不稳定,约8M

可直接作为系统时钟的选择(如图:系统时钟源有4个来源选择,后边讲解)

可2分频后经过选择器做PLL时钟源

2. HSE:高速外部时钟

由外部时钟源产生,可接4M-16MHz晶振

可经过选择器1,选择器2做PLL时钟源

可2分频后经过选择器1,选择器2做PLL时钟源

可直接作为系统时钟的时钟源

可128分频后做RTC时钟源

3. PLL:锁相环

作用:可关闭或倍频2-16倍,共16种选择(最大不能超过72MHz)

倍频后的PLLCLK可直接做系统时钟源

可经过USB预分频器(分频前48或72MHz)分频后,做USB时钟(48MHz)

例如:HSE外接8M晶振通过选择器1选择器2进入PLL,可设置PLL的倍频系数(通过配置相关寄存器配置)

倍频后产生的PLLCLK可作为系统时钟的一个选择

4. LSE:低速外部时钟

由外部晶振产生,一般外接32.768MHz晶振给RTC(STM32芯片内部时钟单元)时钟提供时钟源

外接32.768KHz晶振为RTC时钟提供时钟源

5. LSI:低速内部时钟

由内部RC振荡器产生,频率不稳定 约40KHz

为STM32独立看门狗单元提供时钟来源

也可为RTC提供时钟来源(RTC有3个可选时钟源)

由于RTC实时时钟对时钟的要求较高,所以一般不使用LSI作为时钟源,采用LSE外接32.768KHz晶振作为RTC时钟源

三,STM32的八个时钟

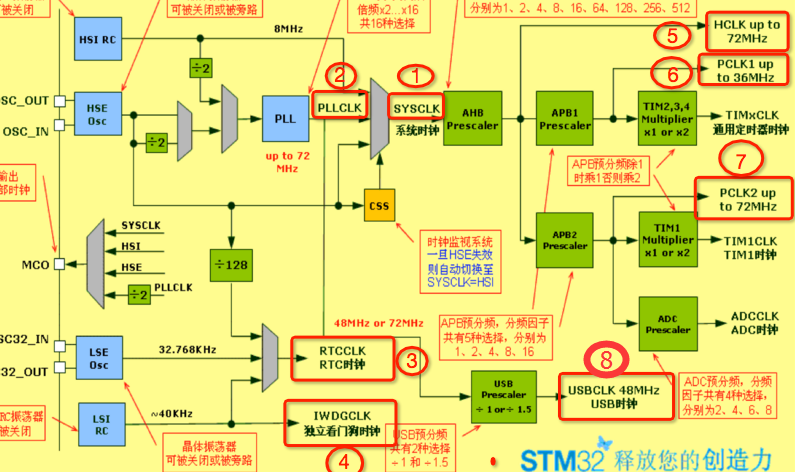

1. 系统时钟-SYSCLK

系统时钟的来源:

1,HSI直接做系统时钟源

2,HSE直接做系统时钟源

3,PLL倍频后的PLLCLK做系统时钟源(这里的PLL时钟来源有3种,一会儿说)

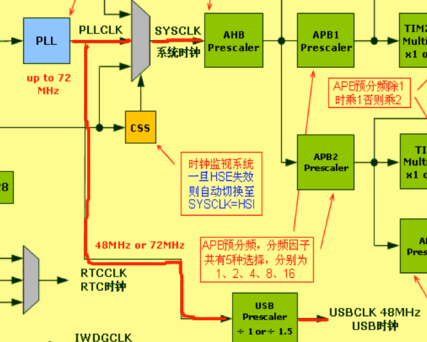

4,CSS单元(时钟监控系统)

CSS作用是监听系统时钟是否出了问题(间接知道外部晶振是否坏了)

项目中大多系统时钟来源采用HSE,一旦监控到HSE失败,会自动切换系统时钟源为HSI

2. PLL时钟-PLLCLK

PLL的时钟来源:

1,HSI的2分频

2,HSE->选择器1->选择器2

3,HSE的2分频->经过选择器1->选择器2

3. RTC时钟-RTCCLK:32.768MHz

RTC时钟来源:

1,HSE的128分频

2,LSE外接32.768kHz晶振

3,LSI直接做RTC时钟源

由于LSI是由内部RC振荡器产生,不稳定,RTC时钟对时钟源的要求较高,多以一般用LSE外接32.768MHz晶振做RTC时钟源

4,独立看门狗时钟-IWDGCLK:40MHz

独立看门狗时钟来源:

由LSI直接作为其时钟源

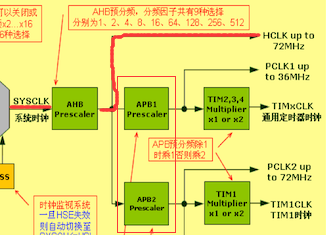

5. AHB总线时钟-HCLK:速度最高72MHz

AHB预分频器,9种分频因子为:1,2,4,8,16,64,128,256,512

系统时钟HCLK 经过AHB预分频器,产生HCLK时钟(最高72M)

一般将系统时钟设置为72M将AHB预分频器设置为1

AHB总线下还挂载了ABP1预分频器和APB2预分频器(后边说)

6. APB1总线时钟-PCLK1(低速):速度最高36MHz

APB1预分频器:分频因子:1,2,4,8,16

AHB时钟HCLK经过APB1预分频器,产生PCLK1时钟(最高到36M)-低速外设总线时钟

下面挂一些低速外设,如:通用定时器时钟

APB1总线下挂载的部分这里不做讲解(到定时器时再说)

7. APB2总线时钟-PCLK2(高速):速度最高72MHz

APB2预分频器-5种分频因子为:1,2,4,8,16

AHB时钟HCLK经过APB2预分频器,产生PCLK2时钟(最高到72M)-高速外设总线时钟

下面挂一些高速外设,如:TIM1时钟,ADC时钟

APB2总线下挂载的部分这里不做讲解(到定时器和ADC时再说)

8. USB时钟-USBCLK:48MHz

来自PLLCLK经过USB分频器(可通过相关寄存器配置 1倍 1.5倍)

F1芯片在不超频时的最大时钟是72MHz,也就是说:

当PLLCLK为72MHz系统时钟时,USB分频器为1.5倍,72/1.5=48MHz

当PLLCLK为48MHz时,USB分频器为1倍,48/1=48MHz

所以:使用外设前需要使能相应的钟使能位,否则外设不能使用

STM32有很多外设,不使用的不打开,否则增加功耗(耗电)

四,MCO:输出内部时钟的引脚

MCO:输出内部时钟的引脚(PA8),可输出相关内部时钟

MCO输出内部时钟的选择:

SYSCLK-系统时钟

HSI-高速内部时钟

HSE-高速外部时钟

PLLCLK的2分频

五,时钟系统寄存器

与时钟相关的配置寄存器一般在:stm32f10x_rcc.c下stm32f10x_rcc.h头文件中

stm32f10x_rcc.c下stm32f10x.h中包含了大多数的地址映射,可找到RCC结构体

/**

* @brief Reset and Clock Control

*/

typedef struct

{

__IO uint32_t CR; // HSI,HSE,CSS,PLL等的使能和就绪标志位

__IO uint32_t CFGR; // PLL等的时钟源选择,分频系数设定

__IO uint32_t CIR; // 清除/使能 时钟就绪中断

__IO uint32_t APB2RSTR; // APB2线上外设复位寄存器

__IO uint32_t APB1RSTR; // APB1线上外设复位寄存器

__IO uint32_t AHBENR; // DMA,SDIO等时钟使能

__IO uint32_t APB2ENR; // APB2线上外设时钟使能

__IO uint32_t APB1ENR; // APB1线上外设时钟使能

__IO uint32_t BDCR; // 备份域控制寄存器

__IO uint32_t CSR; // 控制状态寄存器

#ifdef STM32F10X_CL

__IO uint32_t AHBRSTR;

__IO uint32_t CFGR2;

#endif /* STM32F10X_CL */

#if defined (STM32F10X_LD_VL) || defined (STM32F10X_MD_VL) || defined (STM32F10X_HD_VL)

uint32_t RESERVED0;

__IO uint32_t CFGR2;

#endif /* STM32F10X_LD_VL || STM32F10X_MD_VL || STM32F10X_HD_VL */

} RCC_TypeDef;

其中常用的五个寄存器:

__IO uint32_t CR; // HSI,HSE,CSS,PLL等的使能和就绪标志位

__IO uint32_t CFGR; // PLL等的时钟源选择,分频系数设定

__IO uint32_t AHBENR; // DMA,SDIO等时钟使能

__IO uint32_t APB2ENR; // APB2线上外设时钟使能

__IO uint32_t APB1ENR; // APB1线上外设时钟使能

后三个寄存器:

外设时钟使能寄存器-控制AHB,APB1,APB2

例如:

AHB控制SDIO时钟,CRC时钟使能

APB1控制IO口时钟使能

APB1控制串口使能,I2

版权声明:「BraveWangDev」https://blog.csdn.net/ABAP_Brave/article/details/52290784